# System Ready, 20-Bit, ±2LSB INL, Voltage Output DAC

Data Sheet AD5790

#### **FEATURES**

Single 20-bit voltage output DAC, ±2 LSB INL 8 nV/√Hz output noise spectral density 0.1 LSB long-term linearity error stability ±0.018 ppm/°C gain error temperature coefficient 2.5 µs output voltage settling time 3.5 nV-sec midscale glitch impulse Integrated precision reference buffers Operating temperature range: −40°C to +125°C 4 mm × 5 mm LFCSP package Wide power supply range of up to ±16.5 V 35 MHz Schmitt-triggered digital interface 1.8 V compatible digital interface

#### **APPLICATIONS**

Medical instrumentation

Test and measurement

Industrial control

Scientific and aerospace instrumentation

Data acquisition systems

Digital gain and offset adjustment

Power supply control

#### **GENERAL DESCRIPTION**

The AD5790¹ is a single 20-bit, unbuffered voltage-output DAC that operates from a bipolar supply of up to 33 V. The AD5790 accepts a positive reference input in the range of 5 V to  $V_{\rm DD}$  – 2.5 V and a negative reference input in the range of  $V_{\rm SS}$  + 2.5 V to 0 V. The AD5790 offers a relative accuracy specification of  $\pm 2$  LSB maximum range, and operation is guaranteed monotonic with a –1 LSB to +3 LSB DNL specification.

The part uses a versatile 3-wire serial interface that operates at clock rates of up to 35 MHz and is compatible with standard SPI, QSPI™, MICROWIRE™, and DSP interface standards. Reference buffers are also provided on chip. The part incorporates a power-on reset circuit that ensures the DAC output powers up to 0 V in a known output impedance state and remains in this state until a valid write to the device takes place. The part provides a disable feature that places the output in a defined load state. The part provides an output clamp feature that places the output in a defined load state.

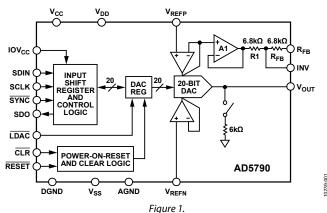

#### FUNCTIONAL BLOCK DIAGRAM

Table 1. Related Devices

| Part No.        | Description                                                             |

|-----------------|-------------------------------------------------------------------------|

| AD5791          | 20-bit, 1 LSB accurate DAC                                              |

| AD5780          | 18-bit, ±1 LSB INL, voltage output DAC ,<br>buffered reference inputs   |

| AD5781          | 18-bit, ±1 LSB INL, voltage Output DAC ,<br>unbuffered reference inputs |

| AD5760          | 16-bit, ±0.5 LSB INL, voltage Output DAC                                |

| AD5541A/AD5542A | 16-bit, 1 LSB accurate 5 V DAC                                          |

#### **PRODUCT HIGHLIGHTS**

- 1. 20-bit resolution.

- 2. Wide power supply range of up to  $\pm 16.5$  V.

- 3.  $-40^{\circ}$ C to  $+125^{\circ}$ C operating temperature range.

- 4. Low 8 nV/ $\sqrt{\text{Hz}}$  noise.

- 5. Low ±0.018 ppm/°C gain error temperature coefficient.

#### **COMPANION PRODUCTS**

Output Amplifier Buffer: AD8675, ADA4898-1, ADA4004-1

External Reference: ADR445

DC-to-DC Design Tool: ADIsimPower™

Additional companion products on the AD5790 product page

$<sup>^{\</sup>mbox{\tiny 1}}$  Protected by U.S. Patent No. 7,884,747.

# **TABLE OF CONTENTS**

| Features                                     |

|----------------------------------------------|

| Applications                                 |

| Functional Block Diagram                     |

| General Description                          |

| Product Highlights                           |

| Companion Products                           |

| Revision History                             |

| Specifications                               |

| Timing Characteristics                       |

| Absolute Maximum Ratings 8                   |

| ESD Caution 8                                |

| Pin Configuration and Function Descriptions9 |

| Typical Performance Characteristics          |

| Terminology                                  |

| Theory of Operation                          |

|                                              |

| REVISION HISTORY                             |

| 2/12—Rev. A to Rev. B                        |

| Deleted Linearity Compensation Section       |

| 12/11—Rev. 0 to Rev. A                       |

| Changes to Table 1                           |

| Changes to Table 2                           |

| Changes to Figure 48                         |

| Changes to DAC Register Section              |

| Updated Outline Dimensions                   |

| _                                            |

| 11/11—Revision 0: Initial Version            |

| DAC Architecture               | 19 |

|--------------------------------|----|

| Serial Interface               | 19 |

| Standalone Operation           | 20 |

| Hardware Control Pins          | 20 |

| On-Chip Registers              | 21 |

| AD5790 Features                | 24 |

| Power-On to 0 V                | 24 |

| Configuring the AD5790         | 24 |

| DAC Output State               | 24 |

| Output Amplifier Configuration | 24 |

| Applications Information       | 26 |

| Typical Operating Circuit      | 26 |

| Evaluation Board               | 27 |

| Outline Dimensions             | 28 |

| Ordering Guide                 | 28 |

# **SPECIFICATIONS**

$V_{\text{DD}} = 12.5 \text{ V to } 16.5 \text{ V}, V_{\text{SS}} = -16.5 \text{ V to } -12.5 \text{ V}, V_{\text{REFP}} = 10 \text{ V}, V_{\text{REFN}} = -10 \text{ V}, V_{\text{CC}} = 2.7 \text{ V to } +5.5 \text{ V}, IOV_{\text{CC}} = 1.71 \text{ V to } 5.5 \text{ V}, R_{\text{L}} = \text{unloaded}, C_{\text{L}} = \text{unloaded}, T_{\text{MIN}} \text{ to } T_{\text{MAX}}, \text{unless otherwise noted}.$

Table 2.

|                                                    |            | B Version | 1          |         |                                                                                                           |  |  |  |  |

|----------------------------------------------------|------------|-----------|------------|---------|-----------------------------------------------------------------------------------------------------------|--|--|--|--|

| Parameter                                          | Min        | Тур       | Max        | Unit    | Test Conditions/Comments                                                                                  |  |  |  |  |

| STATIC PERFORMANCE <sup>2</sup>                    |            |           |            |         |                                                                                                           |  |  |  |  |

| Resolution                                         | 20         |           |            | Bits    |                                                                                                           |  |  |  |  |

| Integral Nonlinearity Error (Relative<br>Accuracy) | -2         | ±1.2      | +2         | LSB     | $V_{REFP} = +10 \text{ V}, V_{REFN} = -10 \text{ V}, T_A = 0^{\circ}\text{C to } 105^{\circ}\text{C}$     |  |  |  |  |

|                                                    | -3         | ±1.2      | +3         | LSB     | $V_{REFP} = +10 \text{ V}, V_{REFN} = -10 \text{ V}, T_A = -40^{\circ}\text{C to } +105^{\circ}\text{C}$  |  |  |  |  |

|                                                    | -4         | ±1.2      | +4         | LSB     | $V_{REFx} = \pm 10 \text{ V}, +10 \text{ V}, \text{ and } +5 \text{ V}$                                   |  |  |  |  |

| Differential Nonlinearity Error                    | -1         |           | +2         | LSB     | $V_{REFP} = +10 \text{ V}, V_{REFN} = -10 \text{ V}, T_A = 0^{\circ}\text{C to } 105^{\circ}\text{C}$     |  |  |  |  |

|                                                    | -1         |           | +3         | LSB     | $V_{REFx} = \pm 10 \text{ V}, +10 \text{ V}, \text{ and } +5 \text{ V}$                                   |  |  |  |  |

| Long-Term Linearity Error Stability <sup>3</sup>   |            | 0.1       |            | LSB     | After 750 hours at T <sub>A</sub> = 135°C                                                                 |  |  |  |  |

| Full-Scale Error                                   | -12        | ±3.8      | +12        | LSB     | $V_{REFP} = +10 \text{ V}, V_{REFN} = -10 \text{ V}$                                                      |  |  |  |  |

|                                                    | -22        | ±2.7      | +22        | LSB     | $V_{REFP} = 10 \text{ V}, V_{REFN} = 0 \text{ V}$                                                         |  |  |  |  |

|                                                    | -40        | ±1.8      | +40        | LSB     | $V_{REFP} = 5 \text{ V}, V_{REFN} = 0 \text{ V}$                                                          |  |  |  |  |

|                                                    | -9         | ±3.8      | +9         | LSB     | $V_{REFP} = +10 \text{ V}, V_{REFN} = -10 \text{ V}, T_A = 0^{\circ}\text{C to } 105^{\circ}\text{C}$     |  |  |  |  |

|                                                    | -12        | ±2.7      | +12        | LSB     | $V_{REFP} = 10 \text{ V}, V_{REFN} = 0 \text{ V}, T_A = 0^{\circ}\text{C to } 105^{\circ}\text{C}$        |  |  |  |  |

|                                                    | -22        | ±1.8      | +22        | LSB     | $V_{REFP} = 5 \text{ V}, V_{REFN} = 0 \text{ V}, T_A = 0^{\circ}\text{C} \text{ to } 105^{\circ}\text{C}$ |  |  |  |  |

| Full-Scale Error Temperature Coefficient           |            | ±0.026    |            | ppm/°C  | $V_{REFP} = +10 \text{ V}, V_{REFN} = -10 \text{ V}$                                                      |  |  |  |  |

| Zero-Scale Error                                   | -19        | ±1.3      | +19        | LSB     | $V_{REFP} = +10 \text{ V}, V_{REFN} = -10 \text{ V}$                                                      |  |  |  |  |

|                                                    | -40        | ±0.7      | +40        | LSB     | $V_{REFP} = 10 \text{ V}, V_{REFN} = 0 \text{ V}$                                                         |  |  |  |  |

|                                                    | -82        | ±0.9      | +82        | LSB     | $V_{REFP} = 5 \text{ V}, V_{REFN} = 0 \text{ V}$                                                          |  |  |  |  |

|                                                    | -8         | ±1.3      | +8         | LSB     | $V_{REFP} = +10 \text{ V}, V_{REFN} = -10 \text{ V}, T_A = 0^{\circ}\text{C to } 105^{\circ}\text{C}$     |  |  |  |  |

|                                                    | -13        | ±0.7      | +13        | LSB     | $V_{REFP} = 10 \text{ V}, V_{REFN} = 0 \text{ V}, T_A = 0^{\circ}\text{C to } 105^{\circ}\text{C}$        |  |  |  |  |

|                                                    | -22        | ±0.9      | +22        | LSB     | $V_{REFP} = 5 \text{ V}, V_{REFN} = 0 \text{ V}, T_A = 0^{\circ}\text{C to } 105^{\circ}\text{C}$         |  |  |  |  |

| Zero-Scale Error Temperature Coefficient           |            | ±0.025    |            | ppm/°C  | $V_{REFP} = +10 \text{ V}, V_{REFN} = -10 \text{ V}$                                                      |  |  |  |  |

| Gain Error                                         | -19        | ±2.3      | +19        | ppm FSR | $V_{REFP} = +10 \text{ V}, V_{REFN} = -10 \text{ V}$                                                      |  |  |  |  |

|                                                    | -35        | ±1.9      | +35        | ppm FSR | $V_{REFP} = 10 \text{ V}, V_{REFN} = 0 \text{ V}$                                                         |  |  |  |  |

|                                                    | -68        | ±0.9      | +68        | ppm FSR | $V_{REFP} = 5 \text{ V}, V_{REFN} = 0 \text{ V}$                                                          |  |  |  |  |

|                                                    | -9         | ±2.3      | +9         | ppm FSR | $V_{REFP} = +10 \text{ V}, V_{REFN} = -10 \text{ V}, T_A = 0^{\circ}\text{C to } 105^{\circ}\text{C}$     |  |  |  |  |

|                                                    | -15        | ±2.9      | +15        | ppm FSR | $V_{REFP} = 10 \text{ V}, V_{REFN} = 0 \text{ V}, T_A = 0^{\circ}\text{C to } 105^{\circ}\text{C}$        |  |  |  |  |

|                                                    | -22        | ±0.9      | +22        | ppm FSR | $V_{REFP} = 5 \text{ V}, V_{REFN} = 0 \text{ V}, T_A = 0^{\circ}\text{C to } 105^{\circ}\text{C}$         |  |  |  |  |

| Gain Error Temperature Coefficient                 |            | ±0.018    |            | ppm/°C  | $V_{REFP} = +10 \text{ V}, V_{REFN} = -10 \text{ V}$                                                      |  |  |  |  |

| R1, R <sub>FB</sub> Matching                       |            | 0.015     |            | %       |                                                                                                           |  |  |  |  |

| OUTPUT CHARACTERISTICS                             |            |           |            |         |                                                                                                           |  |  |  |  |

| Output Voltage Range                               | $V_{REFN}$ |           | $V_{REFP}$ | V       |                                                                                                           |  |  |  |  |

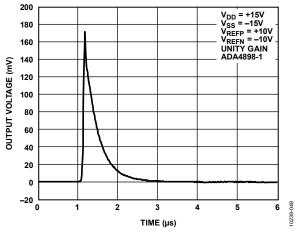

| Output Voltage Settling Time                       |            | 2.5       |            | μs      | 10 V step to 0.02%, using the ADA4898-1 buffer in unity-gain mode                                         |  |  |  |  |

|                                                    |            | 3.5       |            | μs      | 500 code step to ±1 LSB <sup>4</sup>                                                                      |  |  |  |  |

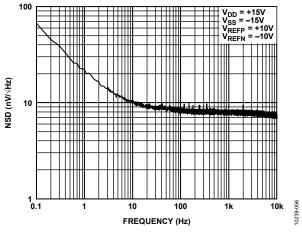

| Output Noise Spectral Density                      |            | 8         |            | nV/√Hz  | At 1 kHz, DAC code = midscale                                                                             |  |  |  |  |

|                                                    |            | 8         |            | nV/√Hz  | At 10 kHz, DAC code = midscale                                                                            |  |  |  |  |

| Output Voltage Noise                               |            | 1.1       |            | μV p-p  | DAC code = midscale, 0.1 Hz to 10 Hz bandwidth                                                            |  |  |  |  |

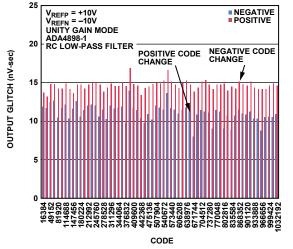

| Midscale Glitch Impulse <sup>4</sup>               |            | 14        |            | nV-sec  | $V_{REFP} = +10 \text{ V}, V_{REFN} = -10 \text{ V}$                                                      |  |  |  |  |

|                                                    |            | 3.5       |            | nV-sec  | $V_{REFP} = 10 \text{ V}, V_{REFN} = 0 \text{ V}$                                                         |  |  |  |  |

|                                                    |            | 4         |            | nV-sec  | $V_{REFP} = 5 \text{ V}, V_{REFN} = 0 \text{ V}$                                                          |  |  |  |  |

| MSB Segment Glitch Impulse <sup>4</sup>            |            | 14        |            | nV-sec  | $V_{REFP} = +10 \text{ V}, V_{REFN} = -10 \text{ V}, \text{ see Figure 43}$                               |  |  |  |  |

| •                                                  |            | 3.5       |            | nV-sec  | $V_{REFP} = 10 \text{ V}, V_{REFN} = 0 \text{ V}, \text{ see Figure 44}$                                  |  |  |  |  |

|                                                    |            | 4         |            | nV-sec  | $V_{REFP} = 5 \text{ V}, V_{REFN} = 0 \text{ V}, \text{ see Figure 45}$                                   |  |  |  |  |

|                                                |                         | B Version | 1                     |        |                                                                            |

|------------------------------------------------|-------------------------|-----------|-----------------------|--------|----------------------------------------------------------------------------|

| Parameter                                      | Min                     | Тур       | Max                   | Unit   | Test Conditions/Comments                                                   |

| Output Enabled Glitch Impulse                  |                         | 57        |                       | nV-sec | On removal of output ground clamp                                          |

| Digital Feedthrough                            |                         | 0.27      |                       | nV-sec |                                                                            |

| DC Output Impedance (Normal Mode)              |                         | 3.4       |                       | kΩ     |                                                                            |

| DC Output Impedance (Output Clamped to Ground) |                         | 6         |                       | kΩ     |                                                                            |

| REFERENCE INPUTS                               |                         |           |                       |        |                                                                            |

| V <sub>REFP</sub> Input Range                  | 5                       |           | $V_{\text{DD}}-2.5$   | V      |                                                                            |

| V <sub>REFN</sub> Input Range                  | V <sub>ss</sub> + 2.5   |           | 0                     | V      |                                                                            |

| Input Bias Current                             | -20                     | -0.63     | +20                   | nA     |                                                                            |

|                                                | -4                      | -0.63     | +4                    |        | $T_A = 0$ °C to $105$ °C                                                   |

| Input Capacitance                              |                         | 1         |                       | pF     | V <sub>REFP</sub> , V <sub>REFN</sub>                                      |

| LOGIC INPUTS                                   |                         |           |                       |        |                                                                            |

| Input Current⁵                                 | -1                      |           | +1                    | μΑ     |                                                                            |

| Input Low Voltage, V <sub>IL</sub>             |                         |           | $0.3 \times IOV_{CC}$ | V      | $IOV_{CC} = 1.71 \text{ V to } 5.5 \text{ V}$                              |

| Input High Voltage, V <sub>IH</sub>            | $0.7 \times IOV_{CC}$   |           |                       | V      | $IOV_{CC} = 1.71 \text{ V to } 5.5 \text{ V}$                              |

| Pin Capacitance                                |                         | 5         |                       | pF     |                                                                            |

| LOGIC OUTPUT (SDO)                             |                         |           |                       |        |                                                                            |

| Output Low Voltage, Vol                        |                         |           | 0.4                   | V      | $IOV_{CC} = 1.71 \text{ V to } 5.5 \text{ V, sinking } 1 \text{ mA}$       |

| Output High Voltage, V <sub>он</sub>           | IOV <sub>CC</sub> - 0.5 |           |                       | V      | $IOV_{CC} = 1.71 \text{ V to } 5.5 \text{ V, sourcing } 1 \text{ mA}$      |

| High Impedance Leakage Current                 |                         |           | ±1                    | μΑ     |                                                                            |

| High Impedance Output Capacitance              |                         | 3         |                       | pF     |                                                                            |

| POWER REQUIREMENTS                             |                         |           |                       |        | All digital inputs at DGND or IOVcc                                        |

| $V_{DD}$                                       | 7.5                     |           | $V_{SS} + 33$         | V      |                                                                            |

| $V_{SS}$                                       | V <sub>DD</sub> - 33    |           | -2.5                  | V      |                                                                            |

| Vcc                                            | 2.7                     |           | 5.5                   | V      |                                                                            |

| IOV <sub>cc</sub>                              | 1.71                    |           | 5.5                   | V      | IOV <sub>CC</sub> ≤ V <sub>CC</sub>                                        |

| I <sub>DD</sub>                                |                         | 10.3      | 14                    | mA     |                                                                            |

| I <sub>SS</sub>                                |                         | -10       | -14                   | mA     |                                                                            |

| Icc                                            |                         | 600       | 900                   | μΑ     |                                                                            |

| IOI <sub>cc</sub>                              |                         | 52        | 140                   | μΑ     | SDO disabled                                                               |

| DC Power Supply Rejection Ratio                |                         | ±7.5      |                       | μV/V   | $\Delta V_{DD} \pm 10\%$ , $V_{SS} = -15 \text{ V}$                        |

|                                                |                         | ±1.5      |                       | μV/V   | $\Delta V_{SS} \pm 10\%, V_{DD} = 15 \text{ V}$                            |

| AC Power Supply Rejection Ratio                |                         | 90        |                       | dB     | $\Delta V_{DD} \pm 200 \text{ mV}$ , 50 Hz/60 Hz, $V_{SS} = -15 \text{ V}$ |

|                                                |                         | 90        |                       | dB     | $\Delta V_{SS} \pm 200 \text{ mV}$ , 50 Hz/60 Hz, $V_{DD} = 15 \text{ V}$  |

$<sup>^{1} \</sup>text{ Temperature range: } -40^{\circ}\text{C to } +125^{\circ}\text{C, typical conditions: } T_{A} = +25^{\circ}\text{C, } V_{DD} = +15 \text{ V, } V_{SS} = -15 \text{ V, } V_{REFP} = +10 \text{ V, } V_{REFN} = -10 \text{ V.} \\ ^{2} \text{ Performance characterized with the AD8675ARZ output buffer.}$

<sup>&</sup>lt;sup>4</sup> The AD5790 is configured in unity-gain mode with a low-pass RC filter on the output. R = 300 Ω, C = 143 pF (total capacitance seen by the output buffer, lead capacitance, and so forth).

<sup>5</sup> Current flowing in an individual logic pin.

# **TIMING CHARACTERISTICS**

$V_{\text{CC}}$  = 2.7 V to 5.5 V; all specifications  $T_{\text{MIN}}$  to  $T_{\text{MAX}}$ , unless otherwise noted.

Table 3.

|                             | Lim | nit <sup>1</sup> |        |                                                                               |

|-----------------------------|-----|------------------|--------|-------------------------------------------------------------------------------|

| Parameter                   |     |                  | Unit   | Test Conditions/Comments                                                      |

| t <sub>1</sub> <sup>2</sup> | 40  | 28               | ns min | SCLK cycle time                                                               |

|                             | 92  | 60               | ns min | SCLK cycle time (readback and daisy-chain modes)                              |

| $t_2$                       | 15  | 10               | ns min | SCLK high time                                                                |

| t <sub>3</sub>              | 9   | 5                | ns min | SCLK low time                                                                 |

| t <sub>4</sub>              | 5   | 5                | ns min | SYNC to SCLK falling edge setup time                                          |

| <b>t</b> <sub>5</sub>       | 2   | 2                | ns min | SCLK falling edge to SYNC rising edge hold time                               |

| t <sub>6</sub>              | 48  | 40               | ns min | Minimum SYNC high time                                                        |

| $t_7$                       | 8   | 6                | ns min | SYNC rising edge to next SCLK falling edge ignore                             |

| t <sub>8</sub>              | 9   | 7                | ns min | Data setup time                                                               |

| t <sub>9</sub>              | 12  | 7                | ns min | Data hold time                                                                |

| t <sub>10</sub>             | 13  | 10               | ns min | LDAC falling edge to SYNC falling edge                                        |

| t <sub>11</sub>             | 20  | 16               | ns min | SYNC rising edge to LDAC falling edge                                         |

| t <sub>12</sub>             | 14  | 11               | ns min | LDAC pulse width low                                                          |

| t <sub>13</sub>             | 130 | 130              | ns typ | LDAC falling edge to output response time                                     |

| t <sub>14</sub>             | 130 | 130              | ns typ | SYNC rising edge to output response time (LDAC tied low)                      |

| t <sub>15</sub>             | 50  | 50               | ns min | CLR pulse width low                                                           |

| t <sub>16</sub>             | 140 | 140              | ns typ | CLR pulse activation time                                                     |

| t <sub>17</sub>             | 0   | 0                | ns min | SYNC falling edge to first SCLK rising edge                                   |

| t <sub>18</sub>             | 65  | 60               | ns max | $\overline{\text{SYNC}}$ rising edge to SDO tristate (C <sub>L</sub> = 50 pF) |

| t <sub>19</sub>             | 62  | 45               | ns max | SCLK rising edge to SDO valid ( $C_L = 50 \text{ pF}$ )                       |

| t <sub>20</sub>             | 0   | 0                | ns min | SYNC rising edge to SCLK rising edge ignore                                   |

| t <sub>21</sub>             | 35  | 35               | ns typ | RESET pulse width low                                                         |

| t <sub>22</sub>             | 150 | 150              | ns typ | RESET pulse activation time                                                   |

$<sup>^1</sup>$  All input signals are specified with  $t_R=t_F=1$  ns/V (10% to 90% of IOV  $_{CC}$ ) and timed from a voltage level of (V  $_{\! L}+V_{\! IH})/2$ .  $^2$  Maximum SCLK frequency is 35 MHz for write mode and 16 MHz for readback and daisy-chain modes.

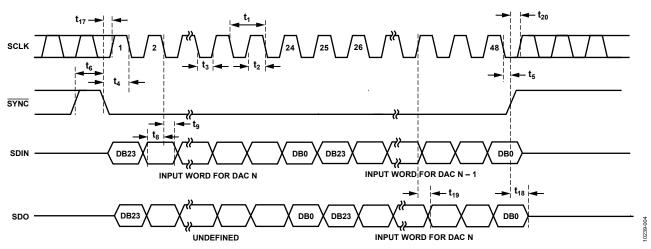

Figure 3. Readback Mode Timing Diagram

Figure 4. Daisy-Chain Mode Timing Diagram

# **ABSOLUTE MAXIMUM RATINGS**

$T_A = 25$ °C, unless otherwise noted.

Transient currents of up to 100 mA do not cause SCR latch-up.

Table 4

| Table 4.                                            |                                                                    |

|-----------------------------------------------------|--------------------------------------------------------------------|

| Parameter                                           | Rating                                                             |

| V <sub>DD</sub> to AGND                             | -0.3 V to +34 V                                                    |

| V <sub>SS</sub> to AGND                             | −34 V to +0.3 V                                                    |

| $V_{DD}$ to $V_{SS}$                                | −0.3 V to +34 V                                                    |

| V <sub>CC</sub> to DGND                             | −0.3 V to +7 V                                                     |

| IOV <sub>cc</sub> to DGND                           | -0.3 V to V <sub>CC</sub> + 3 V or +7 V (whichever is less)        |

| Digital Inputs to DGND                              | -0.3 V to IOV <sub>CC</sub> + 0.3 V or<br>+7 V (whichever is less) |

| Vout to AGND                                        | $-0.3 \text{ V to V}_{DD} + 0.3 \text{ V}$                         |

| V <sub>REFP</sub> to AGND                           | $-0.3 \text{ V to V}_{DD} + 0.3 \text{ V}$                         |

| V <sub>REFN</sub> to AGND                           | $V_{SS} - 0.3 \text{ V to} + 0.3 \text{ V}$                        |

| DGND to AGND                                        | −0.3 V to +0.3 V                                                   |

| Operating Temperature Range, T <sub>A</sub>         |                                                                    |

| Industrial                                          | −40°C to +125°C                                                    |

| Storage Temperature Range                           | −65°C to +150°C                                                    |

| Maximum Junction Temperature,<br>T <sub>J</sub> max | 150°C                                                              |

| Power Dissipation                                   | $(T_J \max - T_A)/\theta_{JA}$                                     |

| LFCSP Package                                       |                                                                    |

| $\theta_{JA}$ Thermal Impedance                     | 31.0°C/W                                                           |

| Lead Temperature                                    | JEDEC industry standard                                            |

| Soldering                                           | J-STD-020                                                          |

| ESD (Human Body Model)                              | 1.6 kV                                                             |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

This device is a high performance integrated circuit with an ESD rating of <1.6 kV, and it is ESD sensitive. Proper precautions must be taken for handling and assembly.

# **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

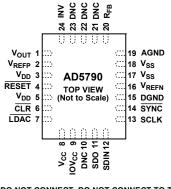

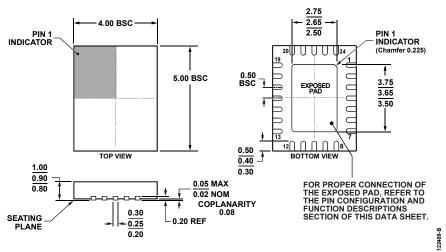

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

NOTES

1. DNC = DO NOT CONNECT. DO NOT CONNECT TO THIS PIN.

2. NEGATIVE ANALOG SUPPLY CONNECTION (VSS).

A VOLTAGE IN THE RANGE OF -16.5 V TO -2.5 V

CAN BE CONNECTED. VSS SHOULD BE DECOUPLED

TO AGND. THE PADDLE CAN BE LEFT ELECTRICALLY

UNCONNECTED PROVIDED THAT A SUPPLY

CONNECTION IS MADE AT THE VSS PINS. IT IS

RECOMMENDED THAT THE PADDLE BE THERMALLY

CONNECTED TO A COPPER PLANE FOR ENHANCED

THERMAL PERFORMANCE.

Figure 5. Pin Configuration

**Table 5. Pin Function Descriptions**

| Pin No.        | Mnemonic          | Description                                                                                                                                                                                                                                                                                                                                                                            |

|----------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1              | V <sub>OUT</sub>  | Analog Output Voltage.                                                                                                                                                                                                                                                                                                                                                                 |

| 2              | V <sub>REFP</sub> | Positive Reference Voltage Input. A voltage in the range of 5 V to $V_{DD}$ – 2.5 V can be connected.                                                                                                                                                                                                                                                                                  |

| 3, 5           | $V_{DD}$          | Positive Analog Supply Connection. A voltage in the range of 7.5 V to 16.5 V can be connected. V <sub>DD</sub> must be decoupled to AGND.                                                                                                                                                                                                                                              |

| 4              | RESET             | Active Low Reset. Asserting this pin returns the AD5790 to its power-on status.                                                                                                                                                                                                                                                                                                        |

| 6              | CLR               | Active Low Input. Asserting this pin sets the DAC register to a user defined value (see Table 12) and updates the DAC output. The output value depends on the DAC register coding that is being used, either binary or twos complement.                                                                                                                                                |

| 7              | LDAC              | Active Low Load DAC Logic Input. This is used to update the DAC register and, consequently, the analog output. When tied permanently low, the output is updated on the rising edge of SYNC. If LDAC is held high during the write cycle, the input register is updated, but the output update is held off until the falling edge of LDAC. The LDAC pin should not be left unconnected. |

| 8              | Vcc               | Digital Supply. Voltage range is from 2.7 V to 5.5 V. V <sub>CC</sub> should be decoupled to DGND.                                                                                                                                                                                                                                                                                     |

| 9              | IOV <sub>CC</sub> | Digital Interface Supply. Digital threshold levels are referenced to the voltage applied to this pin. Voltage range is from 1.71 V to 5.5 V                                                                                                                                                                                                                                            |

| 10, 21, 22, 23 | DNC               | Do Not Connect. Do not connect to these pins.                                                                                                                                                                                                                                                                                                                                          |

| 11             | SDO               | Serial Data Output.                                                                                                                                                                                                                                                                                                                                                                    |

| 12             | SDIN              | Serial Data Input. This device has a 24-bit input shift register. Data is clocked into the register on the falling edge of the serial clock input.                                                                                                                                                                                                                                     |

| 13             | SCLK              | Serial Clock Input. Data is clocked into the input shift register on the falling edge of the serial clock input. Data can be transferred at rates of up to 35 MHz.                                                                                                                                                                                                                     |

| 14             | SYNC              | <u>Level-Triggered Control Input</u> (Active Low). This is the frame synchronization signal for the input data. When <u>SYNC</u> goes low, it enables the input shift register, and data is then transferred in on the falling edges of the following clocks. The DAC is updated on the rising edge of <u>SYNC</u> .                                                                   |

| 15             | DGND              | Ground Reference Pin for Digital Circuitry.                                                                                                                                                                                                                                                                                                                                            |

| 16             | V <sub>REFN</sub> | Negative Reference Voltage Input.                                                                                                                                                                                                                                                                                                                                                      |

| 17, 18         | $V_{SS}$          | Negative Analog Supply Connection. A voltage in the range of $-16.5$ V to $-2.5$ V can be connected. $V_{SS}$ must be decoupled to AGND.                                                                                                                                                                                                                                               |

| 19             | AGND              | Ground Reference Pin for Analog Circuitry.                                                                                                                                                                                                                                                                                                                                             |

| 20             | R <sub>FB</sub>   | Feedback Connection for External Amplifier. See the AD5790 Features section for further details.                                                                                                                                                                                                                                                                                       |

| 24             | INV               | Inverting Input Connection for External Amplifier. See the AD5790 Features section for further details.                                                                                                                                                                                                                                                                                |

| EPAD           | Vss               | Negative Analog Supply Connection ( $V_{55}$ ). A voltage in the range of $-16.5$ V to $-2.5$ V can be connected. $V_{55}$ must be decoupled to AGND. The paddle can be left electrically unconnected provided that a supply connection is made at the $V_{55}$ pins. It is recommended that the paddle be thermally connected to a copper plane for enhanced thermal performance.     |

# TYPICAL PERFORMANCE CHARACTERISTICS

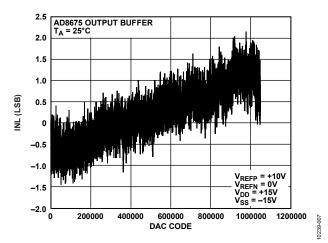

Figure 6. Integral Nonlinearity Error vs. DAC Code, ±10 V Span

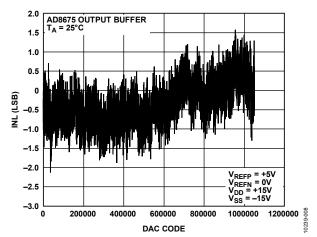

Figure 7. Integral Nonlinearity Error vs. DAC Code, 10 V Span

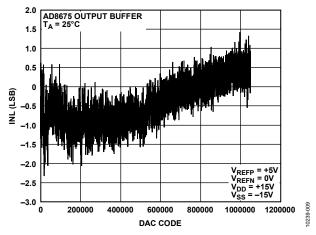

Figure 8. Integral Nonlinearity Error vs. DAC Code, 5 V Span

Figure 9. Integral Nonlinearity Error vs. DAC Code, 5 V Span, ×2 Gain Mode

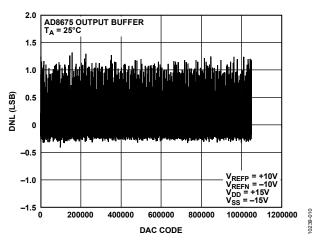

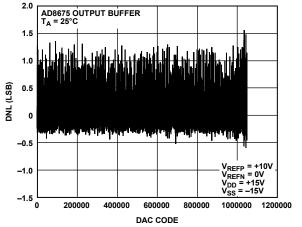

Figure 10. Differential Nonlinearity Error vs. DAC Code,  $\pm 10$  V Span

Figure 11. Differential Nonlinearity Error vs. DAC Code, 10 V Span

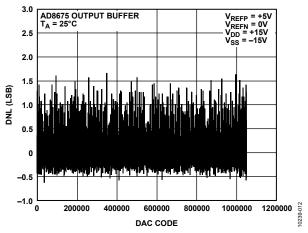

Figure 12. Differential Nonlinearity Error vs. DAC Code, 5 V Span

Figure 13. Differential Nonlinearity Error vs. DAC Code, 5 V Span, ×2 Gain Mode

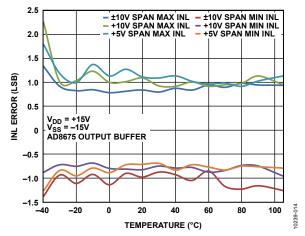

Figure 14. Integral Nonlinearity Error vs. Temperature

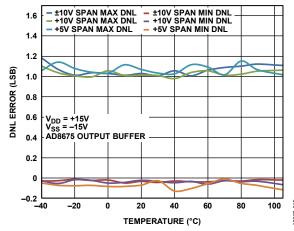

Figure 15. Differential Nonlinearity Error vs. Temperature

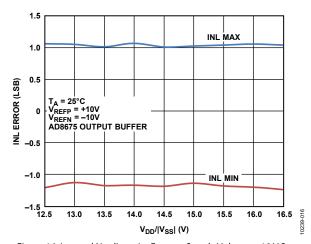

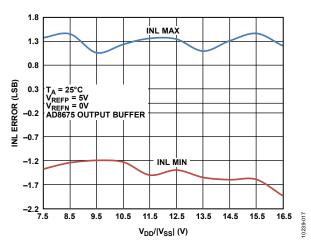

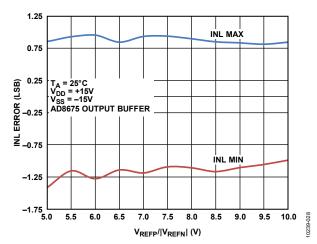

Figure 16. Integral Nonlinearity Error vs. Supply Voltage,  $\pm 10\,\mathrm{V}$  Span

Figure 17. Integral Nonlinearity Error vs. Supply Voltage, 5 V Span

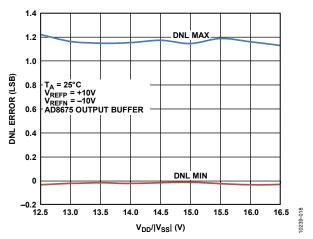

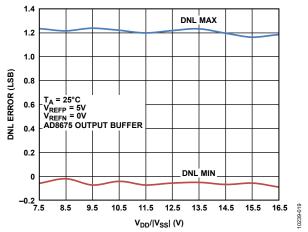

Figure 18. Differential Nonlinearity Error vs. Supply Voltage,  $\pm 10 \text{ V}$  Span

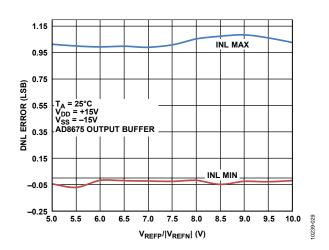

Figure 19. Differential Nonlinearity Error vs. Supply Voltage, 5 V Span

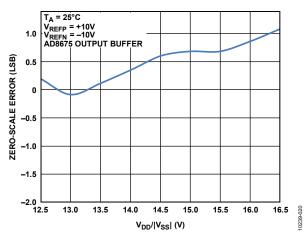

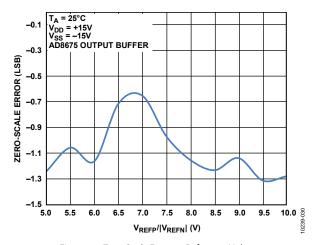

Figure 20. Zero-Scale Error vs. Supply Voltage, ±10 V Span

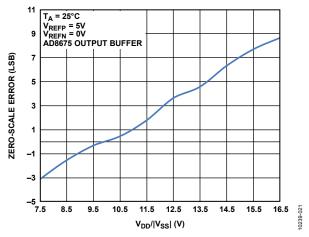

Figure 21. Zero-Scale Error vs. Supply Voltage, 5 V Span

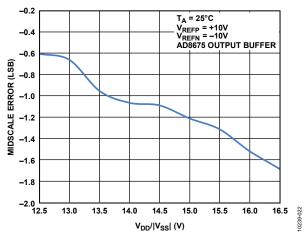

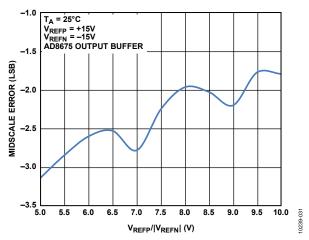

Figure 22. Midscale Error vs. Supply Voltage, ±10 V Span

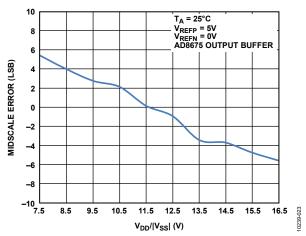

Figure 23. Midscale Error vs. Supply Voltage, 5 V Span

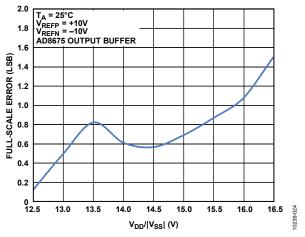

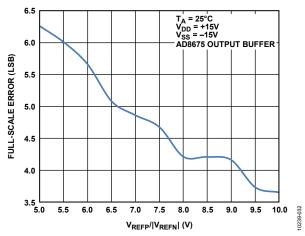

Figure 24. Full-Scale Error vs. Supply Voltage, ±10 V Span

Figure 25. Full-Scale Error vs. Supply Voltage, 5 V Span

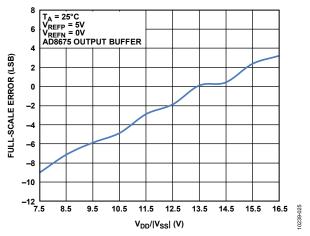

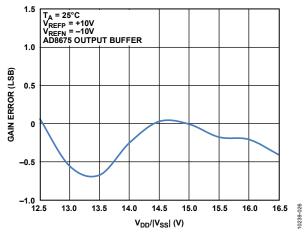

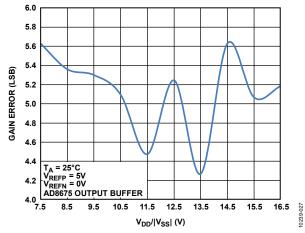

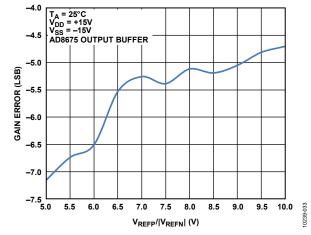

Figure 26. Gain Error vs. Supply Voltage, ±10 V Span

Figure 27. Gain Error vs. Supply Voltage, 5 V Span

Figure 28. Integral Nonlinearity Error vs. Reference Voltage

Figure 29. Differential Nonlinearity Error vs. Reference Voltage

Figure 30. Zero-Scale Error vs. Reference Voltage

Figure 31. Midscale Error vs. Reference Voltage

Figure 32. Full-Scale Error vs. Reference Voltage

Figure 33. Gain Error vs. Reference Voltage

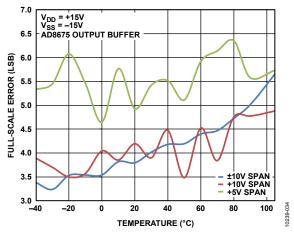

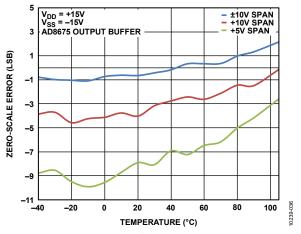

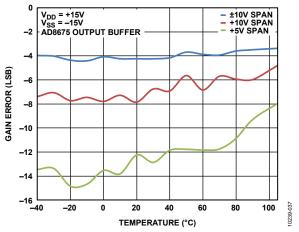

Figure 34. Full-Scale Error vs. Temperature

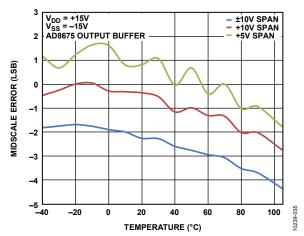

Figure 35. Midscale Error vs. Temperature

Figure 36. Zero-Scale Error vs. Temperature

Figure 37. Gain Error vs. Temperature

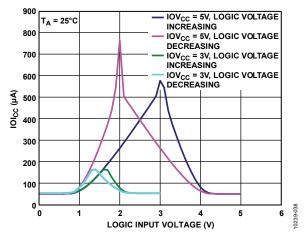

Figure 38. IOIcc vs. Logic Input Voltage

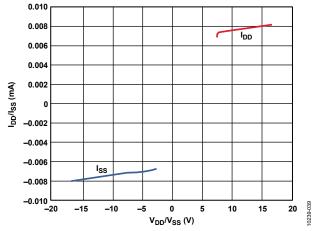

Figure 39. Power Supply Currents vs. Power Supply Voltages

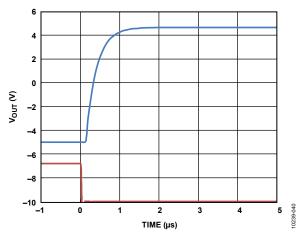

Figure 40. Rising Full-Scale Voltage Step

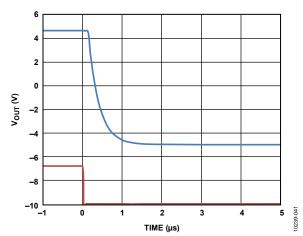

Figure 41. Falling Full-Scale Voltage Step

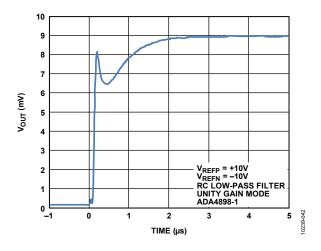

Figure 42. 500 Code Step Settling Time

Figure 43. 6 MSB Segment Glitch Energy for  $\pm 10 \, \text{V}$  V<sub>REF</sub>

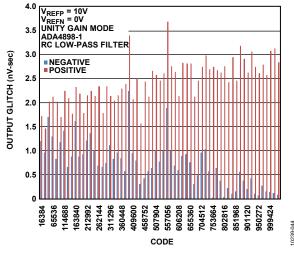

Figure 44. 6 MSB Segment Glitch Energy for 10 V VREF

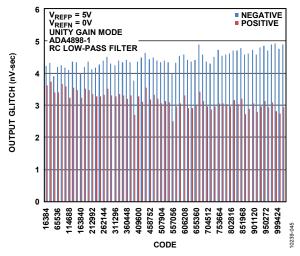

Figure 45. 6 MSB Segment Glitch Energy for 5 V VREF

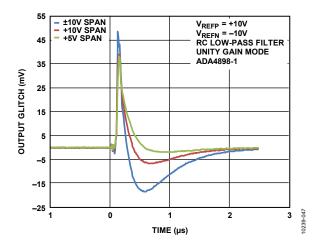

Figure 46. Midscale Peak-to-Peak Glitch for  $\pm 10 \, \mathrm{V}$

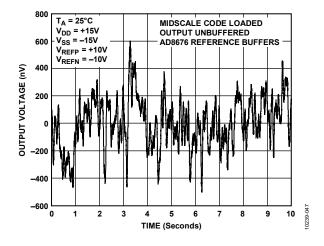

Figure 47. Voltage Output Noise, 0.1 Hz to 10 Hz Bandwidth

Figure 48. Noise Spectral Density vs. Frequency

Figure 49. Glitch Impulse on Removal of Output Clamp

# **TERMINOLOGY**

# **Relative Accuracy**

Relative accuracy, or integral nonlinearity (INL), is a measure of the maximum deviation, in LSB, from a straight line passing through the endpoints of the DAC transfer function. A typical INL error vs. code plot is shown in Figure 6.

#### Differential Nonlinearity (DNL)

Differential nonlinearity is the difference between the measured change and the ideal 1 LSB change between any two adjacent codes. A specified differential nonlinearity of  $\pm 1$  LSB maximum ensures monotonicity. This DAC is guaranteed monotonic. A typical DNL error vs. code plot is shown in Figure 10.

#### **Long-Term Linearity Error Stability**

Linearity error long-term stability is a measure of the stability of the linearity of the DAC over a long period of time. It is specified in LSB for a time period of 500 hours and 1000 hours at an elevated ambient temperature.

#### **Zero-Scale Error**

Zero-scale error is a measure of the output error when zero-scale code (0x00000) is loaded to the DAC register. Ideally, the output voltage should be  $V_{\text{REFN}}$ . Zero-scale error is expressed in LSBs.

#### **Zero-Scale Error Temperature Coefficient**

Zero-scale error temperature coefficient is a measure of the change in zero-scale error with a change in temperature. It is expressed in ppm FSR/°C.

#### **Full-Scale Error**

Full-scale error is a measure of the output error when full-scale code (0x3FFFF) is loaded to the DAC register. Ideally, the output voltage should be  $V_{\text{REFP}}-1$  LSB. Full-scale error is expressed in LSBs.

# **Full-Scale Error Temperature Coefficient**

Full-scale error temperature coefficient is a measure of the change in full-scale error with a change in temperature. It is expressed in ppm FSR/°C.

#### **Gain Error**

Gain error is a measure of the span error of the DAC. It is the deviation in slope of the DAC transfer characteristic from the ideal, expressed in ppm of the full-scale range.

# **Gain Error Temperature Coefficient**

Gain error temperature coefficient is a measure of the change in gain error with a change in temperature. It is expressed in ppm FSR/°C.

#### **Midscale Error**

Midscale error is a measure of the output error when midscale code (0x20000) is loaded to the DAC register. Ideally, the output voltage should be  $(V_{\text{REFP}} - V_{\text{REFN}})/2 + V_{\text{REFN}}$ . Midscale error is expressed in LSBs.

#### **Output Voltage Settling Time**

Output voltage settling time is the amount of time it takes for the output voltage to settle to a specified level for a specified change in voltage. For fast settling applications, a high speed buffer amplifier is required to buffer the load from the 3.4 k $\Omega$  output impedance of the AD5790, in which case, it is the amplifier that determines the settling time.

## Digital-to-Analog Glitch Impulse

Digital-to-analog glitch impulse is the impulse injected into the analog output when the input code in the DAC register changes state. It is specified as the area of the glitch in nV-s and is measured when the digital input code is changed by 1 LSB at the major carry transition. See Figure 49.

## **Output Enabled Glitch Impulse**

Output enabled glitch impulse is the impulse injected into the analog output when the clamp to ground on the DAC output is removed. It is specified as the area of the glitch in nV-sec (see Figure 49).

#### Digital Feedthrough

Digital feedthrough is a measure of the impulse injected into the analog output of the DAC from the digital inputs of the DAC but is measured when the DAC output is not updated. It is specified in nV-sec and measured with a full-scale code change on the data bus, that is, from all 0s to all 1s, and vice versa.

#### **Total Harmonic Distortion (THD)**

Total harmonic distortion is the ratio of the rms sum of the harmonics of the DAC output to the fundamental value. Only the second to fifth harmonics are included.

#### DC Power Supply Rejection Ratio

DC power supply rejection ratio is a measure of the rejection of the output voltage to dc changes in the power supplies applied to the DAC. It is measured for a given dc change in power supply voltage and is expressed in  $\mu V/V$ .

#### AC Power Supply Rejection Ratio (AC PSRR)

AC power supply rejection ratio is a measure of the rejection of the output voltage to ac changes in the power supplies applied to the DAC. It is measured for a given amplitude and frequency change in power supply voltage and is expressed in decibels.

# THEORY OF OPERATION

The AD5790 is a high accuracy, fast settling, single, 20-bit, serial input, voltage-output DAC. It operates from a  $V_{\rm DD}$  supply voltage of 7 V to 16.5 V and a  $V_{\rm SS}$  supply of -16.5 V to -2.5 V. Data is written to the AD5790 in a 24-bit word format via a 3-wire serial interface. The AD5790 incorporates a power-on reset circuit that ensures the DAC output powers up to 0 V with the  $V_{\rm OUT}$  pin clamped to AGND through a  $\sim$ 6 k $\Omega$  internal resistor.

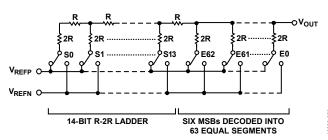

#### **DAC ARCHITECTURE**

The architecture of the AD5790 consists of two matched DAC sections. A simplified circuit diagram is shown in Figure 50. The six MSBs of the 20-bit data-word are decoded to drive 63 switches, E0 to E62. Each of these switches connects one of 63 matched resistors to either the buffered  $V_{\text{REFP}}$  or buffered  $V_{\text{REFN}}$  voltage. The remaining 14 bits of the data-word drive Switches S0 to S13 of a 14-bit voltage mode R-2R ladder network.

Figure 50. DAC Ladder Structure

#### **SERIAL INTERFACE**

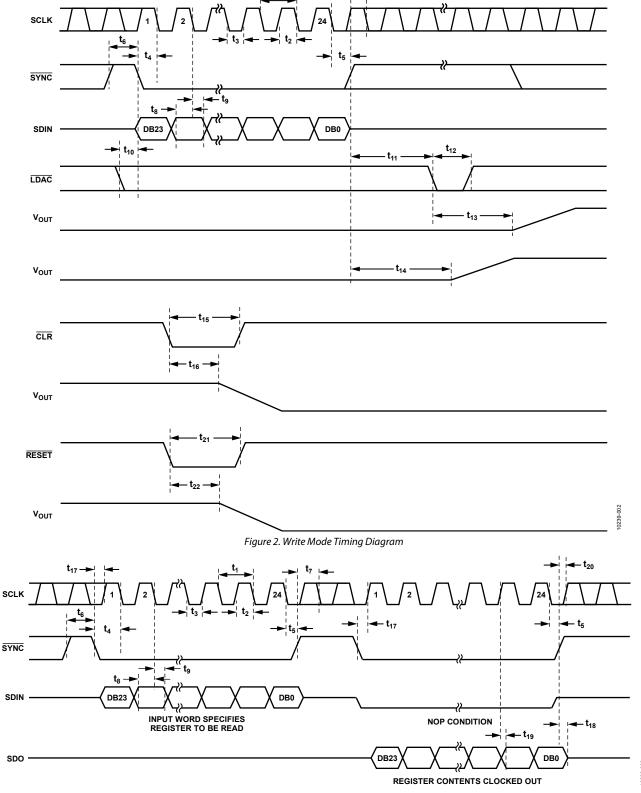

The AD5790 has a 3-wire serial interface (SYNC, SCLK, and SDIN) that is compatible with SPI, QSPI, and MICROWIRE interface standards, as well as most DSPs (see Figure 2 for a timing diagram).

## **Input Shift Register**

The input shift register is 24 bits wide. Data is loaded into the device MSB first as a 24-bit word under the control of a serial clock input, SCLK, which can operate at up to 35 MHz. The input register consists of a  $R/\overline{W}$  bit, three address bits and 20 data bits as shown in Table 6. The timing diagram for this operation is shown in Figure 2.

**Table 6. Input Shift Register Format**

MSB

LSB

DB23

DB22

DB21

DB20

DB19 to DB0

R/W

Register address

Register data

Table 7. Decoding the Input Shift Register

| R/W | Registe | er Addre | ss | Description                                      |

|-----|---------|----------|----|--------------------------------------------------|

| X1  | 0 0 0   |          |    | No operation (NOP). Used in readback operations. |

| 0   | 0 0 1   |          |    | Write to the DAC register.                       |

| 0   | 0 1 0   |          |    | Write to the control register.                   |

| 0   | 0       | 1        | 1  | Write to the clearcode register.                 |

| 0   | 1       | 0        | 0  | Write to the software control register.          |

| 1   | 0 0 1   |          | 1  | Read from the DAC register.                      |

| 1   | 0       | 1        | 0  | Read from the control register.                  |

| 1   | 0       | 1        | 1  | Read from the clearcode register.                |

<sup>&</sup>lt;sup>1</sup> X is don't care.

#### STANDALONE OPERATION

The serial interface works with both a continuous and noncontinuous serial clock. A continuous SCLK source can be used only if SYNC is held low for the correct number of clock cycles.

In gated clock mode, a burst clock containing the exact number of clock cycles must be used, and  $\overline{SYNC}$  must be taken high after the final clock to latch the data. The first falling edge of  $\overline{SYNC}$  starts the write cycle. Exactly 24 falling clock edges must be applied to SCLK before  $\overline{SYNC}$  is brought high again. If  $\overline{SYNC}$  is brought high before the 24<sup>th</sup> falling SCLK edge, the data written is invalid. If more than 24 falling SCLK edges are applied before  $\overline{SYNC}$  is brought high, the input data is also invalid.

The input shift register is updated on the <u>rising</u> edge of SYNC. For another serial transfer to take place,  $\overline{\text{SYNC}}$  must be brought low again. After the end of the serial data transfer, data is automatically transferred from the input shift register to the addressed register. When the write cycle is <u>complete</u>, the output can be updated by taking  $\overline{\text{LDAC}}$  low while  $\overline{\text{SYNC}}$  is high.

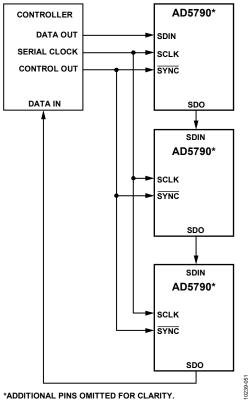

## **Daisy-Chain Operation**

For systems that contain several devices, the SDO pin can be used to daisy chain several devices together. Daisy-chain mode can be useful in system diagnostics and in reducing the number of serial interface lines. The first falling edge of SYNC starts the write cycle. SCLK is continuously applied to the input shift register when SYNC is low. If more than 24 clock pulses are applied, the data ripples out of the shift register and appears on the SDO line. This data is clocked out on the rising edge of SCLK and is valid on the falling edge. By connecting the SDO of the first device to the SDIN input of the next device in the chain, a multidevice interface is constructed. Each device in the system requires 24 clock pulses. Therefore, the total number of clock cycles must equal  $24 \times N$ , where N is the total number of AD5790 devices in the chain. When the serial transfer to all devices is complete, SYNC is taken high. This latches the input data in each device in the daisy chain and prevents any further data from being clocked into the input shift register. The serial clock can be a continuous or a gated clock.

A continuous SCLK source can be used only if SYNC is held low for the correct number of clock cycles. In gated clock mode, a burst clock containing the exact number of clock cycles must be used, and SYNC must be taken high after the final clock to latch the data.

In any one daisy-chain sequence, do not mix writes to the DAC register with writes to any of the other registers. All writes to the daisy-chained parts must be either writes to the DAC registers or writes to the control, clearcode, or software control register.

Figure 51. Daisy-Chain Block Diagram

#### Readback

The contents of all the on-chip registers can be read back via the SDO pin. Table 7 outlines how the registers are decoded. After a register has been addressed for a read, the next 24 clock cycles clock the data out on the SDO pin. The clocks must be applied while \$\overline{SYNC}\$ is low. When \$\overline{SYNC}\$ is returned high, the SDO pin is placed in tristate. For a read of a single register, the NOP function can be used to clock out the data. Alternatively, if more than one register is to be read, the data of the first register to be addressed can be clocked out at the same time the second register to be read is being addressed. The SDO pin must be enabled to complete a readback operation. The SDO pin is enabled by default.

## **HARDWARE CONTROL PINS**

## Load DAC Function (LDAC)

After data has been transferred into the input register of the DAC, there are two ways to update the DAC register and DAC output. Depending on the status of both SYNC and LDAC, one of two update modes is selected: synchronous DAC update or asynchronous DAC update.

#### **Synchronous DAC Update**

In this mode,  $\overline{\text{LDAC}}$  is held low while data is being clocked into the input shift register. The DAC output is updated on the rising edge of  $\overline{\text{SYNC}}$ .

# Asynchronous DAC Update

In this mode,  $\overline{\text{LDAC}}$  is held high while data is being clocked into the input shift register. The DAC output is asynchronously updated by taking  $\overline{\text{LDAC}}$  low after  $\overline{\text{SYNC}}$  has been taken high. The update now occurs on the falling edge of  $\overline{\text{LDAC}}$ .

#### Reset Function (RESET)

The AD5790 can be reset to its power-on state by two means: either by asserting the RESET pin or by using the software reset control function (see Table 13). If the RESET pin is not used, hardwire it to IOV<sub>CC</sub>.

## Asynchronous Clear Function (CLR)

The  $\overline{\text{CLR}}$  pin is an active low clear that allows the output to be cleared to a user defined value. The 20-bit clear code value is programmed to the clearcode register (see Table 12). It is necessary to maintain  $\overline{\text{CLR}}$  low for a minimum amount of time to complete the operation (see Figure 2). When the  $\overline{\text{CLR}}$  signal is returned high the output remains at the clear value (if  $\overline{\text{LDAC}}$  is high) until a new value is loaded to the DAC register. The

output cannot be updated with a new value while the  $\overline{\text{CLR}}$  pin is low. A clear operation can also be performed by setting the CLR bit in the software control register (see Table 13).

#### **ON-CHIP REGISTERS**

#### **DAC Register**

Table 9 outlines how data is written to and read from the DAC register.

The following equation describes the ideal transfer function of the DAC:

$$V_{OUT} = \frac{\left(V_{REFP} - V_{REFN}\right) \times D}{2^{20}} + V_{REFN}$$

where

$V_{REFN}$  is the negative voltage applied at the V<sub>REFP</sub> input pin.  $V_{REFP}$  is the positive voltage applied at the V<sub>REFP</sub> input pin. D is the 20-bit code programmed to the DAC.

**Table 8. Hardware Control Pins Truth Table**

| LDAC  | CLR            | RESET | Function                                                                                        |

|-------|----------------|-------|-------------------------------------------------------------------------------------------------|

| X1    | X <sup>1</sup> | 0     | The AD5790 is in reset mode. The device cannot be programmed.                                   |

| $X^1$ | X <sup>1</sup> | Ţ     | The AD5790 is returned to its power-on state. All registers are set to their default values.    |

| 0     | 0              | 1     | The DAC register is loaded with the clearcode register value and the output is set accordingly. |

| 0     | 1              | 1     | The output is set according to the DAC register value.                                          |

| 1     | 0              | 1     | The DAC register is loaded with the clearcode register value and the output is set accordingly. |

| J     | 1              | 1     | The output is set according to the DAC register value.                                          |

| J     | 0              | 1     | The output remains at the clearcode register value.                                             |

| Ĺ     | 1              | 1     | The output remains set according to the DAC register value.                                     |

| Ĺ     | 0              | 1     | The output remains at the clearcode register value.                                             |

| 1     | l              | 1     | The DAC register is loaded with the clearcode register value and the output is set accordingly. |

| 0     | l              | 1     | The DAC register is loaded with the clearcode register value and the output is set accordingly. |

| 1     | t              | 1     | The output remains at the clearcode register value.                                             |

| 0     | Ĺ              | 1     | The output is set according to the DAC register value.                                          |

<sup>&</sup>lt;sup>1</sup> X is don't care.

Table 9. DAC Register

MSB LSB

| DB23 | DB22 | DB21             | DB20              | DB19 to DB0     |

|------|------|------------------|-------------------|-----------------|

| R/W  |      | Register address | DAC register data |                 |

| R/W  | 0    | 0                | 1                 | 20 bits of data |

# **Control Register**

The control register controls the mode of operation of the AD5790.

# Clearcode Register

The clearcode register sets the value to which the DAC output is set when the  $\overline{CLR}$  pin or CLR bit in the software control register is asserted. The output value depends on the DAC coding that is being used, either binary or twos complement. The default register value is 0.

# **Table 10. Control Register**

MSB LSB

| DB23 | DB22 | DB21      | DB20 | DB19 to DB11 | DB10             | DB9 | DB8 | DB7 | DB6 | DB5    | DB4     | DB3    | DB2   | DB1  | DB0      |

|------|------|-----------|------|--------------|------------------|-----|-----|-----|-----|--------|---------|--------|-------|------|----------|

| R/W  | Reg  | ister add | ress |              | Control register |     |     |     |     |        | ta      |        |       |      |          |

| R/W  | 0    | 1         | 0    | Reserved     | Reserved         |     | 00  | 00  |     | SDODIS | BIN/2sC | DACTRI | OPGND | RBUF | Reserved |

**Table 11. Control Register Functions**

| Bit Name | Description                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Reserved | These bits are reserved and should be programmed to zero.                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| RBUF     | Output amplifier configuration control.                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

|          | 0: the internal amplifier, A1, is powered up and Resistors R <sub>FB</sub> and R1 are connected in series, as shown in Figure 54. This allows an external amplifier to be connected in a gain of two configuration. See the AD5790 Features section for further details.                                                                                                                                                                  |  |  |  |  |

|          | 1: (default) the internal amplifier, A1, is powered down and Resistors $R_{FB}$ and R1 are connected in parallel, as shown in Figure 53, so that the resistance between the $R_{FB}$ and INV pins is 3.4 k $\Omega$ , equal to the resistance of the DAC. This allows the $R_{FB}$ and INV pins to be used for input bias current compensation for an external unity-gain amplifier. See the AD5790 Features section for further details. |  |  |  |  |

| OPGND    | Output ground clamp control.                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|          | 0: the DAC output clamp to ground is removed and the DAC is placed in normal mode.                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|          | 1: (default) the DAC output is clamped to ground through a $\sim$ 6 k $\Omega$ resistance, and the DAC is placed in tristate mode. Resetting the part puts the DAC in OPGND mode, where the output ground clamp is enabled and the DAC is tristated. Setting the OPGND bit to 1 in the control register overrules any write to the DACTRI bit.                                                                                            |  |  |  |  |

| DACTRI   | DAC tristate control.                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

|          | 0: the DAC is in normal operating mode.                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

|          | 1: (default) DAC is in tristate mode.                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| BIN/2sC  | DAC register coding selection.                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

|          | 0: (default) the DAC register uses twos complement coding.                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

|          | 1: the DAC register uses offset binary coding.                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| SDODIS   | SDO pin enable/disable control.                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

|          | 0: (default) the SDO pin is enabled.                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

|          | 1: the SDO pin is disabled (tristate).                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| R/W      | Read/write select bit.                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

|          | 0: AD5790 is addressed for a write operation.                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

|          | 1: AD5790 is addressed for a read operation.                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

# Table 12. Clearcode Register

MSB LSB

| DB23 | DB22 DB21 DB20   |   | DB20 | DB19 to DB0             |

|------|------------------|---|------|-------------------------|

| R/W  | Register address |   |      | Clearcode register data |

| R/W  | 0                | 1 | 1    | 20 bits of data         |

# **Software Control Register**

This is a write only register in which writing a 1 to a particular bit has the same effect as pulsing the corresponding pin low.

# **Table 13. Software Control Register**

MSB LSB

| DB23 | DB22             | DB21 | DB20 | DB19 to DB3                    | DB2   | DB1              | DB0               |

|------|------------------|------|------|--------------------------------|-------|------------------|-------------------|

| R/W  | Register address |      |      | Software control register data |       |                  |                   |

| 0    | 1                | 0    | 0    | Reserved                       | Reset | CLR <sup>1</sup> | LDAC <sup>2</sup> |

$<sup>^{1}</sup>$  The CLR function has no effect when the  $\overline{\text{LDAC}}$  pin is low.

# **Table 14. Software Control Register Functions**

| Bit Name | Description                                                                                                                                                                                                              |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LDAC     | Setting this bit to 1 updates the DAC register and consequently the DAC output.                                                                                                                                          |

| CLR      | Setting this bit to 1 sets the DAC register to a user defined value (see Table 12) and updates the DAC output. The output value depends on the DAC register coding that is being used, either binary or twos complement. |

| Reset    | Setting this bit to 1 returns the AD5790 to its power-on state.                                                                                                                                                          |

$<sup>^2</sup>$  The LDAC function has no effect when the  $\overline{\text{CLR}}$  pin is low.

# **AD5790 FEATURES**

#### POWER-ON TO 0 V

The AD5790 contains a power-on reset circuit that, as well as resetting all registers to their default values, controls the output voltage during power-up. Upon power-on, the DAC is placed in tristate (its reference inputs are disconnected), and its output is clamped to AGND through a  $\sim$ 6 k $\Omega$  resistor. The DAC remains in this state until programmed otherwise via the control register. This is a useful feature in applications where it is important to know the state of the DAC output while it is in the process of powering up.

# **CONFIGURING THE AD5790**

After power-on, the AD5790 must be configured to put it into normal operating mode before programming the output. To do this, the control register must be programmed. The DAC is removed from tristate by clearing the DACTRI bit, and the output clamp is removed by clearing the OPGND bit. At this point, the output goes to  $V_{\text{REFN}}$ , unless an alternative value is first programmed to the DAC register.

#### **DAC OUTPUT STATE**

The DAC output can be placed in one of three states, controlled by the DACTRI and OPGND bits of the control register, as shown in Table 15.

Table 15. Output State Truth Table

| DACTRI | OPGND | Output State                                      |

|--------|-------|---------------------------------------------------|

| 0      | 0     | Normal operating mode                             |

| 0      | 1     | Output is clamped via ~6 kΩ to AGND               |

| 1      | 0     | Output is in tristate                             |

| 1      | 1     | Output is clamped via $\sim$ 6 k $\Omega$ to AGND |

#### **OUTPUT AMPLIFIER CONFIGURATION**

There are a number of different ways that an output amplifier can be connected to the AD5790, depending on the voltage references applied and the desired output voltage span.

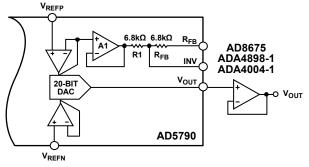

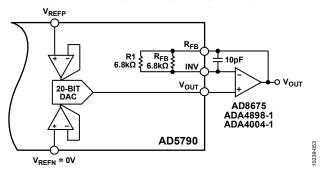

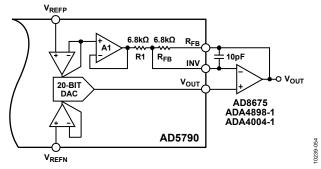

#### **Unity-Gain Configuration**

Figure 52 shows an output amplifier configured for unity gain. In this configuration, the output spans from  $V_{\text{REFN}}$  to  $V_{\text{REFP}}$ .

Figure 52. Output Amplifier in Unity-Gain Configuration

A second unity-gain configuration for the output amplifier is one that removes an offset from the input bias currents of the amplifier. It does this by inserting a resistance in the feedback path of the amplifier that is equal to the output resistance of the DAC. The DAC output resistance is 3.4 k $\Omega$ . By connecting R1 and R<sub>FB</sub> in parallel, a resistance equal to the DAC resistance is available on chip. Because the resistors are all on one piece of silicon, they are temperature coefficient matched. To enable this mode of operation the RBUF bit of the control register must be set to Logic 1. Figure 53 shows how the output amplifier is connected to the AD5790. In this configuration, the output amplifier is in unity gain and the output spans from V<sub>REFN</sub> to V<sub>REFN</sub>. This unity-gain configuration allows a capacitor to be placed in the amplifier feedback path to improve dynamic performance.

Figure 53. Output Amplifier in Unity Gain with Amplifier Input Bias Current Compensation

# Gain of Two Configuration (×2 Gain Mode)

Figure 54 shows an output amplifier configured for a gain of two. The gain is set by the internal matched 6.8 k $\Omega$  resistors, which are exactly twice the DAC resistance, having the effect of removing an offset from the input bias current of the external amplifier. In this configuration, the output spans from 2 ×  $V_{\text{REFN}} - V_{\text{REFP}}$  to  $V_{\text{REFP}}$ . This configuration is used to generate a bipolar output span from a single ended reference input with  $V_{\text{REFN}} = 0$  V. For this mode of operation, the RBUF bit of the control register must be cleared to Logic 0.

Figure 54. Output Amplifier in Gain of Two Configuration

# APPLICATIONS INFORMATION

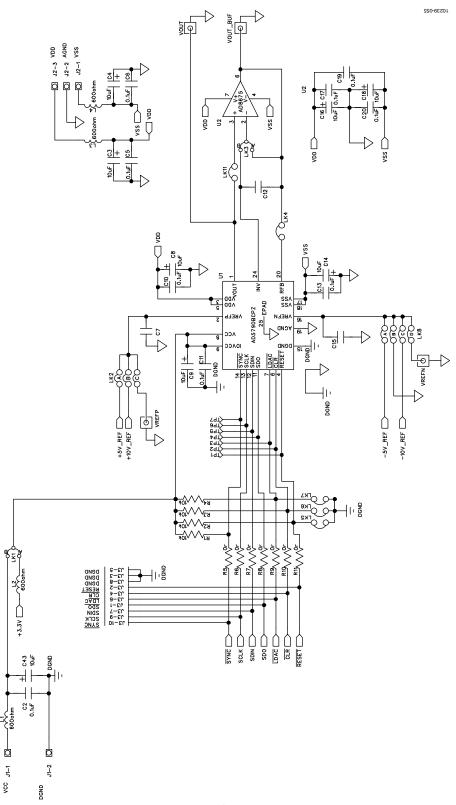

# **TYPICAL OPERATING CIRCUIT**

Figure 55. Typical Operating Circuit

Figure 55 shows a typical operating circuit for the AD5790 using an AD8675 as an output buffer. Because the output impedance of the AD5790 is 3.4 k $\Omega$ , an output buffer is required for driving low resistive, high capacitive loads.

## **EVALUATION BOARD**